previous INTRODUCTION TO DIFFERENT GATE PULSES

3.1 MICROCONTROLLER

Depending on the power and features that are needed, one might choose a 4 bit, 16 bit, or 32 bit microcontroller. In addition, some specialized versions are available which include features specific for communications, keyboard handling, signal processing, video processing, and other tasks.

PIC micro devices are grouped by the size of their Instruction Word. The three current PIC micro families are:

The high performance of the PIC micro TM devices can be attributed to a number of architectural features commonly found in RISC microprocessors:

Harvard Architecture

3.1.5.1 HIGH PERFOTMANCE RISC CPU

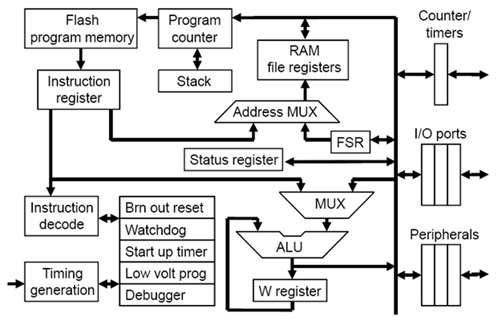

There are two memory blocks in the PIC16F72 device. These are the program memory and the data memory. Each block has separate buses so that concurrent access can occur. Program memory can be read internally by the user code. The data memory can further be broken down into the general purpose RAM and the Special Function Registers (SFRs). The SFRs control the “core”. The SFRs used to control the peripheral modules.

PIC16F72 devices have a 13-bit program counter capable of addressing a 8K x 14 program memory space. The address range for this program memory is 0000h - 07FFh. Accessing a location above the physically implemented address will cause a wraparound. The RESET Vector is at 0000h and the Interrupt Vector is at 0004h.

The Data Memory is partitioned into multiple banks that contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits. Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain SFRs. Some “high use” SFRs from one bank may be mirrored in another bank, for code reduction and quicker access (e.g., the STATUS register is in Banks 0 - 3).

3.1.7 STACK

The stack allows a combination of up to eight program calls and interrupts to occur. The stack contains the return address from this branch in program execution. Mid-range devices have an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSH’d onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POP’d in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSH’d or POP’d. After the stack has been PUSH’d eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

3.1.8 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

3.1.8.1 PORTA AND THE TRISA REGISTER

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). Reading the PORTA register, reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the port data latch. Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1). The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

3.1.8.2 PORTB AND THE TRISB REGISTER

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB’s pins, RB7:RB4, have an interrupt-on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The “mismatch” outputs of RB7:RB4 are OR’d together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin). PORTC is multiplexed with several peripheral functions. PORTC pins have Schmitt Trigger input buffers. When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

The Timer0 module timer/counter has the following features:

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving Operating modes and offer code protection:

The PIC16F72 differentiates between various kinds of RESET:

3.1.11 MCLR

PIC16F72 device has a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses. It should be noted that a WDT Reset does not drive MCLR pin low. The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD.

3.1.12 INTERRUPTS

The PIC16F72 has up to eight sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits. A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt’s flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET. The “return from interrupt” instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts. The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register. The peripheral interrupt flags are contained in the Special Function Register, PIR1. The corresponding interrupt enable bits are contained in Special Function Register, PIE1, and the peripheral interrupt enable bit is contained in Special Function Register INTCON. When an interrupt is serviced, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack, and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupts, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs, relative to the current Q cycle. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or the GIE bit. [13]

3.1.13 APPLICATION OF MICROCONTROLLER

These circuits consist of four independent, high gain, internally frequency compensated operational amplifiers .They operate from a single power supply over a wide range of voltages. Operation from split power supplies is also possible and the low power supply current drain is independent of the magnitude of the power supply voltage. [14]

3.2.1 SPECIFICATIONS

3.1 MICROCONTROLLER

A Microcontroller is a Microcomputer in a single Chip. That means that a microcontroller chip includes a microprocessor (CPU) as well as some often used peripherals. A controller is used to control some process or aspect of the environment. A typical microcontroller application is the monitoring a house. As the temperature rises, the controller causes the windows to open. If the temperature goes above a certain threshold, the air conditioner is activated.

As the process of miniaturization continued, all of the components needed for a controller were built right onto one chip. A one chip computer or microcontroller was born. A microcontroller is a highly integrated chip, which includes, on one chip, all or most of the parts needed for a controller. The microcontroller could be called a “one-chip-solution”. It typically includes:

- CPU (Central Processing Unit or the microprocessor)

- EEPROM / EPROM / PROM / ROM (Read Only Memory for the program code)

- RAM (Random, Access Memory for the program code)

- I /O (Input / Output) devices (serial, parallel, ADC, DAC etc.)

- Timers

- Interrupt controller

- Embedded Controller

- ADC

- Calculator

- PWM function generator

In addition to control applications such as the above home monitoring system, microcontrollers are frequently found in embedded applications. Among many uses that we can find one or more microcontrollers appliances (microwave oven, refrigerators, television and VCRs, stereos), automobiles (engine control, diagnostic, climate control), environmental control (greenhouse, factory, home), instrumentation, aerospace, power electronic controlling and thousands of other uses.

A special application that microcontrollers are well suited for is data logging. Stick one of these chips out in the middle of a paddy field or up in a balloon, and monitor and record environmental parameters (temperature, humidity, rain, etc.). Small size, low power consumption, and flexibility make these devices ideal for unattended data monitoring and recoding. Depending on the power and features that are needed, one might choose a 4 bit, 16 bit, or 32 bit microcontroller. In addition, some specialized versions are available which include features specific for communications, keyboard handling, signal processing, video processing, and other tasks.

3.1.2 PROGRAMMABLE INTEGRATED CIRCUIT (PIC)

PIC controllers are a family of small RISC controllers used in embedded applications. PIC controllers are produced by the company "Microchip”. Literature can be obtained from the Microchip web site. The growth of the 8-bit MCU market share is a testament to the PIC micro MCUs ability to meet the needs of many. This growth has made the PIC micro architecture one of the top three architectures available in the general market today. This growth was fueled by the Microchip vision of the benefits of a low cost OTP solution. Some of the benefits for the customer include:PIC micro devices are grouped by the size of their Instruction Word. The three current PIC micro families are:

- Base-line: 12-bit Instruction Word length

- Mid-Range: 14-bit Instruction Word length

- High-End: 16-bit Instruction Word length

The high performance of the PIC micro TM devices can be attributed to a number of architectural features commonly found in RISC microprocessors:

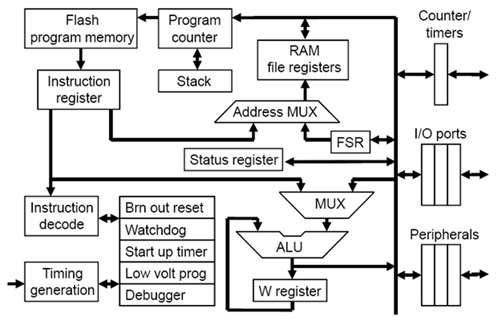

- Harvard architecture

- Long Word Instructions

- Single Word Instructions .Single Cycle Instructions .Instruction Pipelining

- Reduced Instruction Set

- Register File Architecture

- Orthogonal (Symmetric) Instructions

Harvard Architecture

Harvard architecture has the program memory and data memory as separate memories and is accessed from separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. To execute an instruction, a von Neumann machine must make one or more (generally more) accesses across the 8-bit bus to fetch the instruction. Then data may need to be fetched, operated on, and possibly written. As can be seen from this description, that bus can be extremely busy. While with a Harvard architecture, the instruction is fetched in a single instruction cycle (all 14-bits). While the program memory is being accessed, the data memory is on an independent bus and can be read and written. These separated buses allow one instruction to execute while the next instruction is fetched. [12]

Figure 3.1: A typical PIC microcontroller Architecture.

3.1.4 PIC16F72 MICROCONTROLLER

The PIC16F72 belongs to the Mid-Range family of the PIC micro devices. A block diagram of the device is shown in Figure 3.2. The program memory contains 2K words, which translate to 2048 instructions, since each 14-bit program memory word is the same width as each device instruction. The data memory (RAM) contains 128 bytes. There are 22 I/O pins that are user configurable on a pin-to-pin basis. Some pins are multiplexed with other device functions. These functions include:

- External interrupt

- Change on PORTB interrupt

- Timer0 clock input

- Timer1 clock/oscillator

- Capture/Compare/PWM

- A/D converter

- SPI/I2C

Figure 3.2: PIC16F72 Architecture.

3.1.5 PIC16F72 DEVICE INCLUDED3.1.5.1 HIGH PERFOTMANCE RISC CPU

- Only 35 single word instructions to learn

- All single cycle instructions except for program branches, which are two-cycle

- Operating speed: DC - 20 MHz clock input DC - 200 ns instruction cycle

- 2K x 14 words of Program Memory, 128 x 8 bytes of Data Memory (RAM)

- Pin out compatible to PIC16C72/72A and PIC16F872

- Interrupt capability

- Eight-level deep hardware stack

- Direct, Indirect and Relative Addressing modes

- High Sink/Source Current: 25 mA

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler, can be incremented during SLEEP via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Capture, Compare, PWM (CCP) module

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

- PWM max. resolution is 10-bit

- 8-bit, 5-channel analog-to-digital converter

- Synchronous Serial Port (SSP) with SPI™ (Master/Slave) and I2C™ (Slave)

- Brown-out detection circuitry for Brown-out Reset (BOR)

- Low power, high speed CMOS FLASH technology

- Fully static design

- Wide operating voltage range: 2.0V to 5.5V

- Industrial temperature range

- Low power consumption:

- - < 0.6 mA typical @ 3V, 4 MHz

- 20 μA typical @ 3V, 32 kHz

- < 1 μA typical standby current

Figure 3.3: Pin Configuration of PIC16F72.

3.1.5.5 SPECIAL MICROCONTROLLER FEATURES- 1,000 erase/write cycle FLASH program memory typical

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code protection

- Power saving SLEEP mode

- Selectable oscillator options

- In-Circuit Serial Programming™ (ICSP™) via 2 pins

- Processor read access to program memory

There are two memory blocks in the PIC16F72 device. These are the program memory and the data memory. Each block has separate buses so that concurrent access can occur. Program memory can be read internally by the user code. The data memory can further be broken down into the general purpose RAM and the Special Function Registers (SFRs). The SFRs control the “core”. The SFRs used to control the peripheral modules.

PIC16F72 devices have a 13-bit program counter capable of addressing a 8K x 14 program memory space. The address range for this program memory is 0000h - 07FFh. Accessing a location above the physically implemented address will cause a wraparound. The RESET Vector is at 0000h and the Interrupt Vector is at 0004h.

The Data Memory is partitioned into multiple banks that contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits. Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain SFRs. Some “high use” SFRs from one bank may be mirrored in another bank, for code reduction and quicker access (e.g., the STATUS register is in Banks 0 - 3).

3.1.7 STACK

The stack allows a combination of up to eight program calls and interrupts to occur. The stack contains the return address from this branch in program execution. Mid-range devices have an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSH’d onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POP’d in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSH’d or POP’d. After the stack has been PUSH’d eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

3.1.8 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

3.1.8.1 PORTA AND THE TRISA REGISTER

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). Reading the PORTA register, reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the port data latch. Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1). The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

3.1.8.2 PORTB AND THE TRISB REGISTER

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB’s pins, RB7:RB4, have an interrupt-on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The “mismatch” outputs of RB7:RB4 are OR’d together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- Any read or write of PORTB. This will end the mismatch condition.

- Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared. The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature. This interrupt-on-mismatch feature, together with software configurable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, “Implementing Wake-Up on Key Stroke” (AN552). RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION<6>).

3.1.8.3 PORTC AND THE TRISC REGISTERPORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin). PORTC is multiplexed with several peripheral functions. PORTC pins have Schmitt Trigger input buffers. When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving Operating modes and offer code protection:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

These devices have a Watchdog Timer, which can be enabled or disabled using a configuration bit. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes, and is enabled or disabled using a configuration bit. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. Configuration bits are used to select the desired oscillator mode.

3.1.10 RESETThe PIC16F72 differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

3.1.11 MCLR

PIC16F72 device has a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses. It should be noted that a WDT Reset does not drive MCLR pin low. The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD.

3.1.12 INTERRUPTS

The PIC16F72 has up to eight sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits. A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt’s flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET. The “return from interrupt” instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts. The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register. The peripheral interrupt flags are contained in the Special Function Register, PIR1. The corresponding interrupt enable bits are contained in Special Function Register, PIE1, and the peripheral interrupt enable bit is contained in Special Function Register INTCON. When an interrupt is serviced, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack, and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupts, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs, relative to the current Q cycle. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or the GIE bit. [13]

3.1.13 APPLICATION OF MICROCONTROLLER

- Building control

- Access control

- Temperature sensing

- lighting

- If re detection

- Industrial control

- Process control

- Instrumentation

- Industrial instrumentation

- Metering

- Handheld metering systems

- Motor speed control

- AC motor control

- DC motors

- Steppers

- Automotive

- LIN slave nodes

- Body and convenience electronics

These circuits consist of four independent, high gain, internally frequency compensated operational amplifiers .They operate from a single power supply over a wide range of voltages. Operation from split power supplies is also possible and the low power supply current drain is independent of the magnitude of the power supply voltage. [14]

3.2.1 SPECIFICATIONS

- WIDE GAIN BANDWIDTH : 1.3MHz

- INPUT COMMON-MODE VOLTAGE RANGE INCLUDES GROUND.

- LARGEVOLTAGE GAIN: 100 dB .

- VERY LOWSUPPLY CURRENT/AMPLI: 375 mA .

- LOW INPUT BIAS CURRENT: 20nA

- LOW INPUT OFFSET VOLTAGE: 5mV max.

- LOW INPUT OFFSET CURRENT : 2nA

- WIDE POWER SUPPLY RANGE :

- SINGLE SUPPLY : +3V TO +30V

- DUAL SUPPLIES : ±1.5V TO ±15V

Figure 3.4: Pin configuration of LM 324

3.2.3 SCHEMATIC DIAGRAM

Figure 3.5: Internal schematic of LM 324

next 5 PULSE SINE PWM GENERATION FOR IGBT BASED INVERTER

Thank you for sharing best Engineering subject knowledge Its very valuable and supportive for student.

ReplyDeleteget more: Applications of Microcontroller